多电源电路的可靠性设计方案

随着科学技术的发展,通信系统变得越来越发达,使得通信系统的电路中,大多存在两种以上的电源,实际工程应用中还常有蓄电池提供后备供电的情况,对于这些电路,在电压变化的过程中,可能会引发电路无效复位或上电失败的故障。对此,本文提出了一种实用的解决方案。

目前以硬件描述语言(Verilog 或 VHDL)所完成的电路设计,可以经过简单的综合与布局,快速的烧录至 FPGA 上进行测试,是现代 IC 设计验证的技术主流。这些可编辑元件可以被用来实现一些基本的逻辑门电路(比如AND、OR、XOR、NOT)或者更复杂一些的组合功能比如解码器或数学方程式。在大多数的FPGA里面,这些可编辑的元件里也包含记忆元件例如触发器(Flip-flop)或者其他更加完整的记忆块。

系统设计师可以根据需要通过可编辑的连接把FPGA内部的逻辑块连接起来,就好像一个电路试验板被放在了一个芯片里。一个出厂后的成品FPGA的逻辑块和连接可以按照设计者而改变,所以FPGA可以完成所需要的逻辑功能。

随着通信设备复杂程度的提高,工程应用对设备的可靠性要求也随之提高。各种电源配送方案在工程运用上得到了广泛的应用,由于供电系统的切换,通信设备内各部件将面临一次上电初始化的考验。

电路上电问题分析

现在通信机房大多采用-48V直流电源,而电子元器件一般采用低电压供电,以5V和3.3V最为常见,近几年随着低功耗器件的大量使用,1.5V、1.8V、2.5V电源也被采用。在同时使用多种电源时,可采用多种电源模块,下面就两种典型情况作简单分析。

1.采用多电源模块设计的电路

这种设计一般包括1只48-5V电源模块和1只48-3.3V电源模块。其中5V电源模块主要给电路内5V器件供电;3.3V电源模块主要给电路内FPGA、ASIC供电,以及供给直流电压转换器进行更小电压的转换。这里应当指出,如果采用线性调压器(LDO)进行小电压转换时,上级电压通常采用3.3V,因为常用的1.5V、1.8V、2.5V与5V的压降很大,在进行电压转换的时候将损失更多功率,同时增加系统的散热负担。

对于这种设计,由于不同电源模块的指标差异,存在上电顺序的问题。如果5V达到稳定的时间比3.3V早,那么将可能造成如下问题:

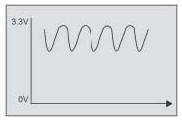

图1: FPGA的上电加载机制。

a. 5V器件已经运行正常,而3.3V的FPGA、ASIC还未加载或初始化完毕。如果电路内MCU单元为5V供电,电路工作将不正常,这种情况理论上可以通过在MCU程序代码里添加空转等待语句,但是实际上仍然存在问题,见下面的分析。

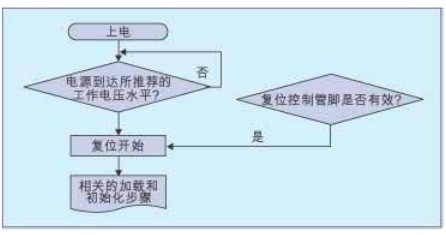

b. FPGA加载失败。图1显示了一般可编程逻辑器件的上电加载机制。图2显示了48-3.3V的某品牌电源模块在用蓄电池加电时,其电压在上升过程中与达到稳定状态前出现的较为严重的波动,测试其他电压,也发现类似情况。从图1、图2可以分析到,FPGA在上电过程中需要自检电压,一旦所有要求的电压值大于某个范围就开始加载,而此时如果电压波动较大,那么FPGA可能会加载失败,因为当波动的电压处于波峰时FPGA快速检查电压并可能通过,当然,现在不少FPGA在上电自检的时候都有个监测电压是否稳定的过程,加载失败的情况基本上很少,不过大部分的FPGA对电压都有严格的要求。

c.与b类似,很多ASIC专用芯片、CPLD在上电初始化的时候都需要有稳定的电压,这里不再累述,可以参阅相关芯片资料。

2.采用单电源模块设计的电路

目前在系统设计中,为了兼容各种电压也常采用48-5V单电源模块和加直流电压转换器的方案。单电源模块也存在上电顺序先后的问题。因此小于5V的电压上电肯定晚于5V.

在蓄电池供电的情况下,由于蓄电池的本身特性,在上电的时候其电压是缓慢上升的,由于现在DC-DC模块的设计差异,某些模块在慢上电的过程中出现的电压摆动仍然会影响FPGA和ASIC的初始化。

解决方法

对应可能出现的问题,可以找到相应的解决方法。在前文分析的第一种情况下,对应a,可以复位MCU;对应b,可以复位FPGA;对应c,可以复位相关芯片。对于第2种情况,复位相应的芯片也可以解决问题。所以最直接有效的方法就是复位。

微处理器用一片或少数几片大规模集成电路组成的中央处理器。这些电路执行控制部件和算术逻辑部件的功能。微处理器与传统的中央处理器相比,具有体积小,重量轻和容易模块化等优点。微处理器的基本组成部分有:寄存器堆、运算器、时序控制电路,以及数据和地址总线。微处理器能完成取指令、执行指令,以及与外界存储器和逻辑部件交换信息等操作,是微型计算机的运算控制部分。它可与存储器和外围电路芯片组成微型计算机。

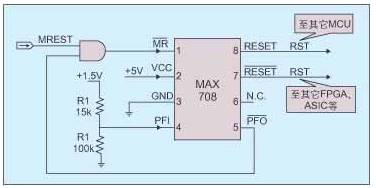

MAX708是一种微处理器电源监控芯片,可同时输出高电平有效和低电平有效的复位信号。复位信号可由VCC 电压、手动复位输入或由独立的比较器触发。因此可以利用MAX708的这个特点来解决电路内MCU、FPGA、ASIC的上电复位问题。

如图3所示,当PFI端子上的电压值小于1.25V时,PFO端子将输出低电平。由于PFI端子的这个特性,可以用它来监控电路上的1.5V电压。在通信设备里,电路上一般含有5V、3.3V、2.5V、1.8V、1.5V的电压值,1.5V应该属于末级电压,就是说通过直流电压转换器最后转压出来的,我们监控了最小电压,自然也就不必理会它的上级电压了。

这里PFI上的电压值大概为1.3V,当然电压值越接近1.25V,电压监控的灵敏度越高。可以用公式{(Vsupply-VPFI)/R1}=(VPFI/R2)计算出需要的电阻比值。这里Vsupply为1.5V,VPFI为1.3V.

可以想象,电路上电过程中,1.5V的末级电压如果没有达到要求,复位信号将一直存在,包括给MCU的RST复位信号,和给其它芯片的低电平有效的复位信号。图3中的MREST为手动添加的复位信号。

需要指出的是,MAX708本身可以监控VCC电压,这对电路采用多电源模块的设计是很有用的。因为两个电源模块相互独立,5V和1.5V可能不是源于同一个电源模块,所以在监控1.5V的同时也需要监控5V电压。

当然,由于MAX708芯片本身的限制,它无法监控小于1.25V的电压。但是在电信级设备中,功耗问题并不很迫切,所以这样小的电压基本上应用很少。

本文小结

电源波动造成的电路上电失败故障,只是涉及电源可靠性的一个方面。这里举的一个实际应用的例子可能并不适合于各种情况,其目的只是在于提醒设计人员在有关电源设计中可能存在的隐患。硬件工程师在应用这些器件进行系统功能设计的同时,也将越来越多的面临如何提高电源可靠性方面的挑战。